Product Summary

The WS62256LLP-70 is a high performance, very low power CMOS static random access memory organized as 32768 words by 8 bits and operates from an very low range of 4.5v to 5.5v supply voltage. The WS62256LLP-70 has an automatic power down feature, reducing the power consumption significantly when chip is deselected.

Parametrics

WS62256LLP-70 absolute maximum ratings: (1)terminal voltage with respect to GND: -5.0 to 6.0v; (2)temperature under bias: -40 to +125℃; (3)storage temperature: -60 to +150℃; (4)power dissipation: 1.0w; (5)DC output current: 20 mA.

Features

WS62256LLP-70 features: (1)operation voltage VCC: 4.5v to 5.5v; (2)very low power consumption: VCC=5.0v: 45mA(max.) write current; 2 mA(max.)read current; 0.4uA(typ.)CMOS standby current; (3)high speed access time: -70 to 70 ns; (4)input levels are CMOS-compatible; (5)automatic power down when chip is deselected; (6)three state outputs; (7)fully static operation; (8)data retention supply voltage as low as 1.5v; (9)easy expansion with CE and OE options; (10)all I/O pins are 5v tolerant.

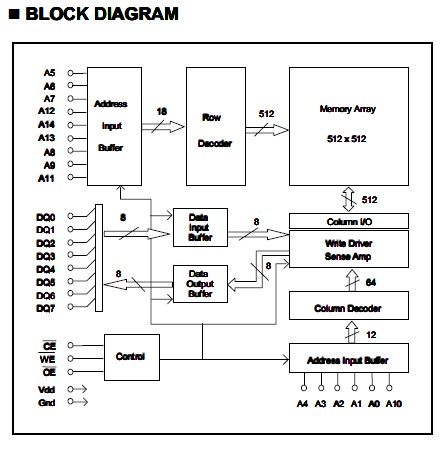

Diagrams

|

WS6264 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))